CA3161

BCD to Seven Segment Decoder/Driver

FN1079 Rev.3.00 Aug 1997

### **Features**

- · TTL Compatible Input Logic Levels

- 25mA (Typ) Constant Current Segment Outputs

- Eliminates Need for Output Current Limiting Resistors

- Pin Compatible with Other Industry Standard Decoders

- Low Standby Power Dissipation ......18mW (Typ)

# **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |  |

|-------------|---------------------|------------|-------------|--|

| CA3161E     | 0 to 70             | 16 Ld PDIP | E16.3       |  |

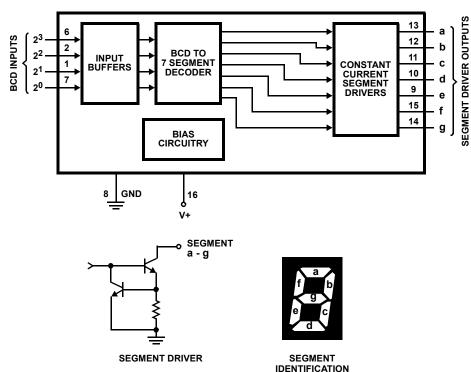

# Description

The CA3161E is a monolithic integrated circuit that performs the BCD to seven segment decoding function and features constant current segment drivers. When used with the CA3162E A/D Converter the CA3161E provides a complete digital readout system with a minimum number of external parts.

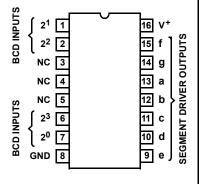

# **Pinout**

CA3161 (PDIP) TOP VIEW

# Functional Block Diagram

## **Absolute Maximum Ratings**

| DC V <sub>SUPPLY</sub> (Between Terminals 1 and 10) | +7.0V |

|-----------------------------------------------------|-------|

| Input Voltage (Terminals 1, 2, 6, 7)                | +5.5V |

| Output Voltage                                      |       |

| Output "Off"                                        | . +7V |

| Output "On" (Note 1)                                | +10V  |

#### Thermal Information

| Thermal Resistance (Typical, Note 2)     | $\theta_{JA}$ (°C/W) |

|------------------------------------------|----------------------|

| PDIP Package                             | 100                  |

| Maximum Junction Temperature             |                      |

| Maximum Storage Temperature Range        | 65°C to 150°C        |

| Maximum Lead Temperature (Soldering 10s) | 300°C                |

### **Operating Conditions**

Temperature Range ......0°C to 75°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. This is the maximum output voltage for any single output. The output voltage must be consistent with the maximum dissipation and derating curve for worst case conditions. Example: All segments "ON", 100% duty cycle.

- 2.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** $T_A = 25 \times {}^{\circ}C$

| PARAMETER                                           | TEST CONDITIONS                       | MIN | TYP | MAX | UNITS |    |

|-----------------------------------------------------|---------------------------------------|-----|-----|-----|-------|----|

| V <sub>SUPPLY</sub> Operating Range, V <sup>+</sup> |                                       | 4.5 | 5   | 5.5 | V     |    |

| Supply Current, I <sup>+</sup> (All Inputs High)    |                                       | -   | 3.5 | 8   | mA    |    |

| Output Current Low (V <sub>O</sub> = 2V)            |                                       | 18  | 25  | 32  | mA    |    |

| Output Current High (V <sub>O</sub> = 5.5V)         |                                       | -   | -   | 250 | μΑ    |    |

| Input Voltage High (Logic "1" Level                 |                                       | 2   | -   | -   | V     |    |

| Input Voltage Low (Logic "0" Level)                 |                                       | -   | -   | 0.8 | V     |    |

| Input Current High (Logic "1")                      |                                       | 2V  | -30 | -   | -     | μΑ |

| Input Current Low (Logic "0")                       |                                       | 0V  | -40 | -   | -     | μΑ |

| Propagation Delay Time,                             | pagation Delay Time, t <sub>PHL</sub> |     | -   | 2.6 | -     | μS |

|                                                     | t <sub>PLH</sub>                      |     | -   | 1.4 | -     | μS |

© Copyright Intersil Americas LLC 1997. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

## TRUTH TABLE

| BINARY |    | INP | UTS |    | OUTPUTS |   |   |   |   |   |   |         |

|--------|----|-----|-----|----|---------|---|---|---|---|---|---|---------|

| STATE  | 23 | 22  | 21  | 20 | а       | b | С | d | е | f | g | DISPLAY |

| 0      | L  | L   | L   | L  | L       | L | L | L | L | L | Н |         |

| 1      | L  | L   | L   | Н  | Н       | L | L | Н | Н | Н | Н |         |

| 2      | L  | L   | Н   | L  | L       | L | Н | L | L | Н | L |         |

| 3      | L  | L   | Н   | Н  | L       | L | L | L | Н | Н | L |         |

| 4      | L  | Н   | L   | L  | Н       | L | L | Н | Н | L | L | 4       |

| 5      | L  | Н   | L   | Н  | L       | Н | L | L | Н | L | L | 5       |

| 6      |    | Н   | Н   | L  | L       | I | L | L | _ | ا | L |         |

| 7      |    | Н   | Н   | Τ  | L       | L | L | I | Н | Н | Τ | (       |

| 8      | Н  | L   | L   | L  | L       | L | L | L | L | L | L |         |

| 9      | Н  | L   | L   | Н  | L       | L | L | L | Н | L | L |         |

| 10     | Н  | L   | Н   | L  | Н       | Н | Н | Н | Н | Н | L | -       |

| 11     | Н  | L   | Н   | Н  | L       | H | Н | L | L | L | L |         |

| 12     | Н  | Н   | L   | L  | Н       | L | L | Н | L | L | L | H       |

| 13     | Н  | Н   | L   | Н  | Н       | Н | Н | L | L | L | Н |         |

| 14     | Н  | Н   | Н   | L  | L       | L | Н | Н | L | L | L |         |

| 15     | Н  | Н   | Н   | Н  | Н       | Н | Н | Н | Н | Н | Н | BLANK   |